News Story

Srivastava is PI; Jacob co-PI for NSF "Unified Framework for 3D CPU Co-Simulation" grant

Professor Ankur Srivastava (ECE/ISR) is the principal investigator for a new National Science Foundation SI2-SSE 3DSIM grant, “A Unified Framework for 3D CPU Co-Simulation.” Professor Bruce Jacob (ECE) is the co-principal investigator.The three-year, $500K grant will allow Srivastava and Jacob to develop a full-system simulator for 3D CPUs that accounts for the architectural and physical interactions between the cores and memory components. This will allow the co-simulation of power, performance and reliability characteristics.

The project will address chip design issues that have come to the fore in recent years. Performance enhancements and increased energy efficiency that previously could be obtained by reducing the dimensions of transistors are becoming more difficult to achieve. Thus, Moore's law no longer holds true for conventional approaches to chip design.

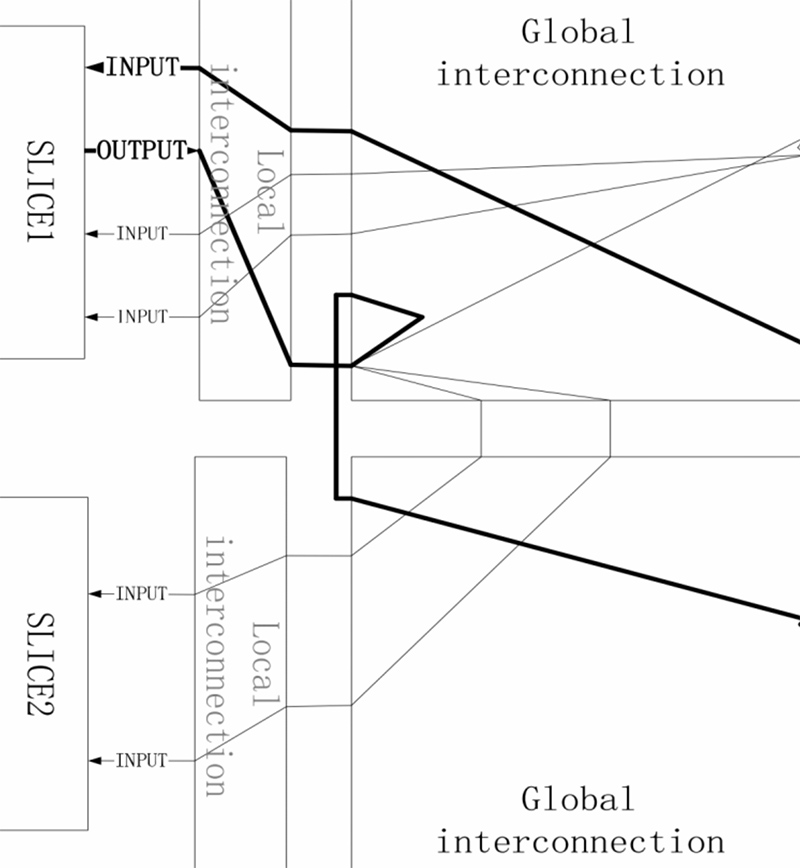

Three-dimensional (3D) integration of chip components has emerged as an innovative packaging alternative to conventional approaches where multiple layers of silicon are stacked and interconnected using directly through the silicon layers (this technique is known as "Through Silicon Via" or TSV). Using TSVs and 3D packaging enables significant benefits to the performance, functionality and energy efficiency of future CPUs. However, 3D integration results in new types of interaction patterns between computing cores and between core and memory components. In addition, the close proximity between cores and memory causes their physical attributes, such as their temperature, noise of power delivery, and reliability to become uniquely interdependent. If innovations in 3D integration are to continue, substantial investment in frameworks that can simulate and evaluate 3D computer architectures are necessary.

This project seeks to develop such a simulation framework and make it available to the computer architecture design community. The researchers’ framework will support a wide array of 3D CPU configurations, including intricate specifications of cores, core counts, network on chip protocols, on-chip/off-chip caches, main memory and off-chip secondary storage (built using diverse set of devices including SRAM, DRAM, non volatile devices). The project is a substantial addition to the repertoire of 3D integrated circuit design and simulation frameworks and will play a vital role in future innovations in 3D CPU architectures.

Published September 8, 2016